基础介绍

TI的RAPIDIO说明链接

串行RapidIO针对高性能嵌入式系统芯片间和板间互连而设计,它将是未来十几年中嵌入式系统互连的最佳选择。

本文比较RapidIO和传统互连技术的优点;介绍RapidIO协议架构,包格式,互连拓扑结构以及串行RapidIO物理层规范。介绍串行RapidIO在无线基础设施方面的应用。

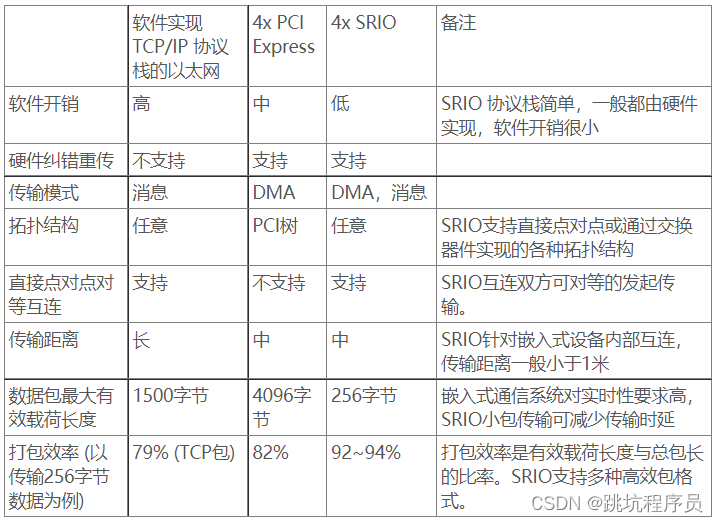

RapidIO 与传统嵌入互连方式的比较

随着高性能嵌入式系统的不断发展,芯片间及板间互连对带宽、成本、灵活性及可靠性的要求越来越高,传统的互连方式,如处理器总线、PCI总线和以太网,都难以满足新的需求 。

协议逻辑层一些说明

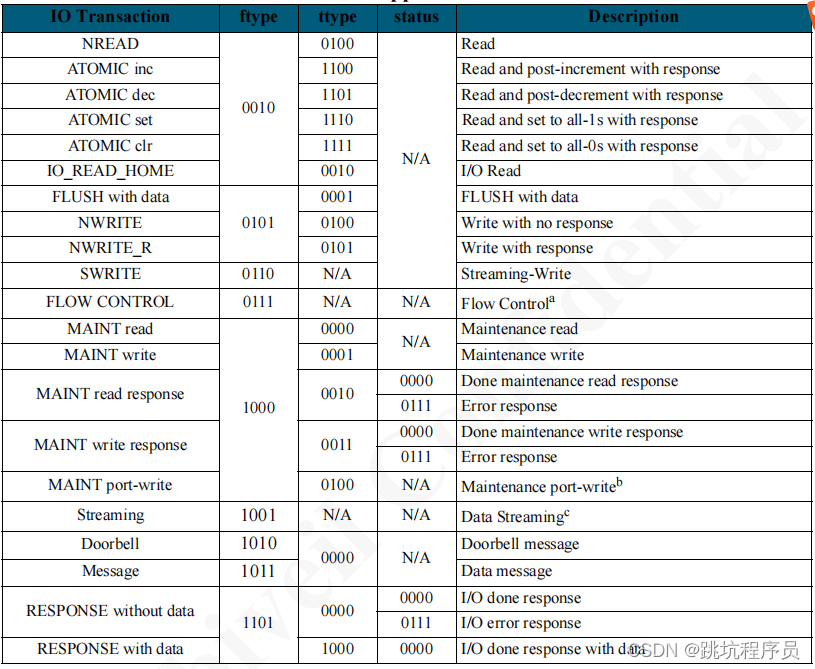

逻辑层定义了操作协议和相应的包格式。RapidIO支持的逻辑层业务主要是:直接IO/DMA (Direct IO/Direct Memory Access)和消息传递(Message Passing)。

直接IO/DMA模式是最简单实用的传输方式,其前提是主设备知道被访问端的存储器映射。在这种模式下,主设备可以直接读写从设备的存储器。直接IO/DMA在被访问端的功能往往完全由硬件实现,所以被访问的器件不会有任何软件负担。

对上层应用来说,发起直接IO/DMA传输主要需提供以下参数:目地器件ID、数据长度、数据在目地器件存储器中的地址。

直接IO/DMA模式又可进一步分为以下几种传输格式:

NWRITE: 写操作,不要求接收端响应。

NWRITE_R: 带响应的NWRITE(NWRITE with Response),要求接收端响应。

SWRITE:流写(Stream Write),数据长度必须是8字节的整数倍,不要求接收端响应。

NREAD: 读操作。

SWRITE是最高效的传输格式;带响应的写操作或读操作效率则较低,一般只能达到不带响应的传输的效率的一半。

消息传递(Message Passing)模式则类似于以太网的传输方式,它不要求主设备知道被访问设备的存储器状况。数据在被访问设备中的位置则由邮箱号(类似于以太网协议中的端口号)确定。从设备根据接收到的包的邮箱号把数据保存到对应的缓冲区,这一过程往往无法完全由硬件实现,而需要软件协助,所以会带来一些软件负担。

对上层应用来说,发起消息传递主要需提供以下参数:目地器件ID、数据长度、邮箱号。

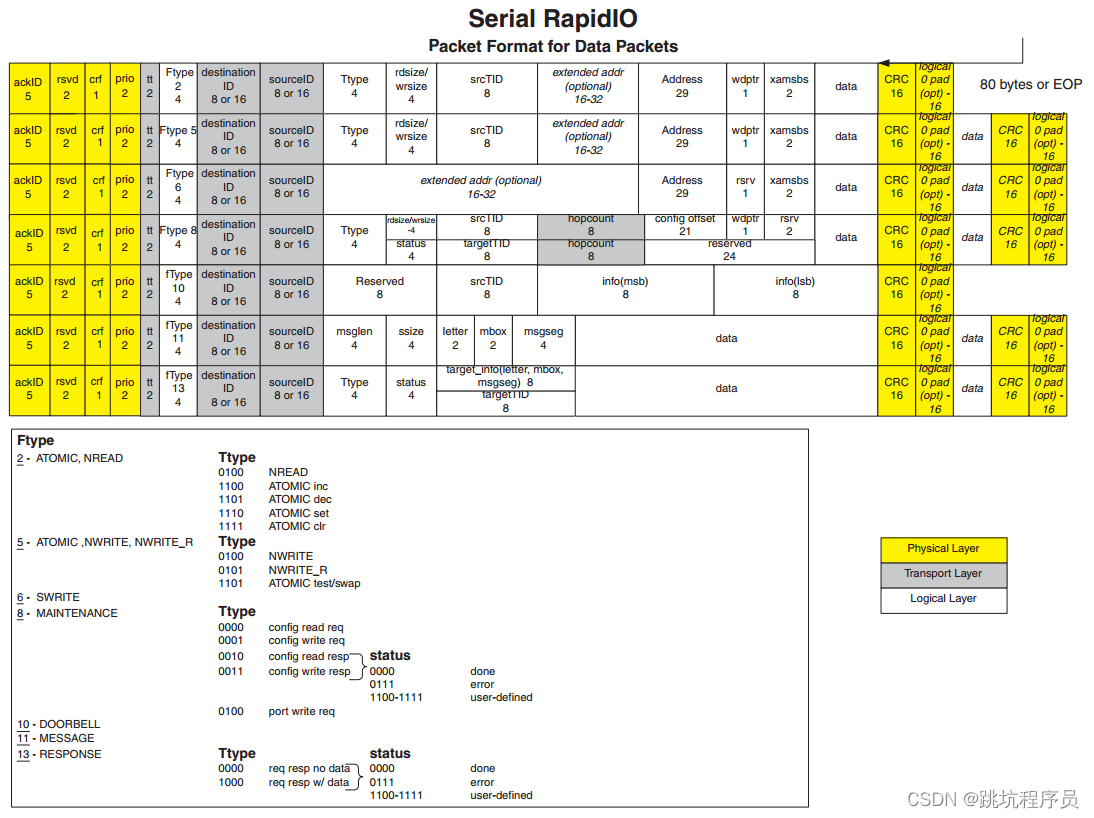

包格式说明

对RAPIDIO的发送数据包格式很好说明的链接

重点是这个图

消息说明连接

我使用设备的相关功能

文档说明

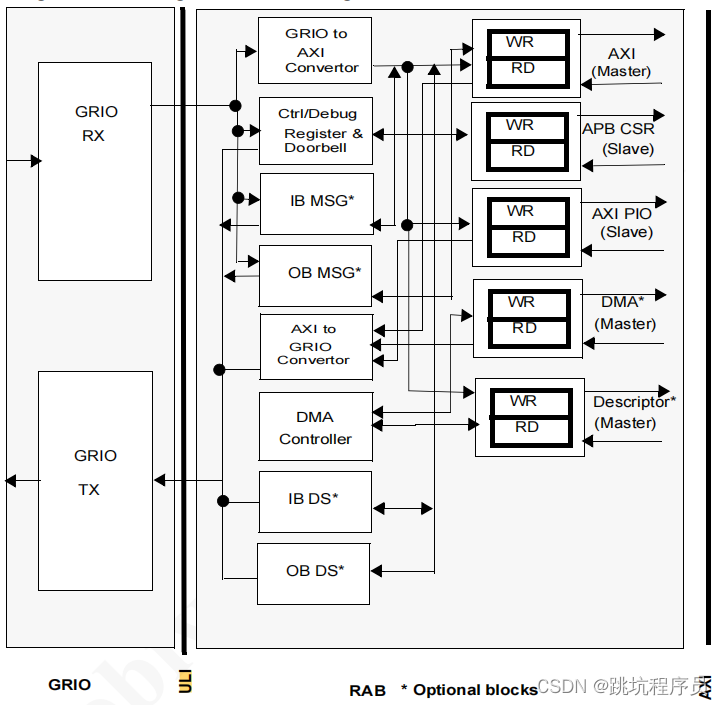

IP文档分为2个部分,分别为GRIO_Datasheet和RapidIO to AXI Bridge Controller_Datasheet,两个文档分别说明整个IP的2个部分功能。从下面图可以明确的区分两个部分,ULI的左边Generic RapidIO Conterllr 简称GRIO右边为RapidIO to AXI Bridge Controller_Datasheet简称RAB。

GRIO (Generic RapidIO Conterllr) 简介

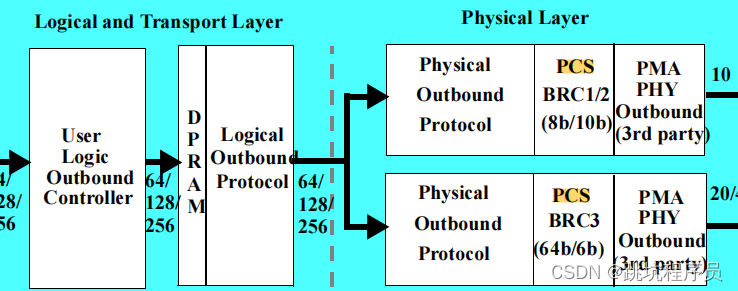

GRIO is partitioned into inbound and outbound blocks, and these blocks are further partitioned into three implementation layers:

1.Physical Layer

2.Logical Layer

对于软件来说该部分主要在初始化阶段会接触到,比如与PHY相关的初始化,链路状态,主从初始化等,后续数据传输基本不用再修改这个部分的设置和寄存器。细节在后续GRIO 程序分析的文章中我再认真分析初始化的相关过程。

从输出方向来看相关的内容,输入方向类似。

RapidIO 互连规范。 物理 PCS 和物理协议层主要解决 RapidIO 互连规范中标题为“LP-Serial Physical层”。 在 GRIO 中,逻辑层实现了逻辑和传输层协议规范。

Physical Layer 物理层

物理层标准的一些知识可以该链接了解一下

SERDES分为PCS(物理编码子层)和PMA(物理媒介附属子层)两层,其中PCS是由纯数字电路组成,可以用软逻辑来实现,而PMA则既包括了数字电路,也包括了模拟电路,不能用纯逻辑实现。

Physical PCS功能

PCS功能

Physical PCS

1.BRC1 and BRC2

• Provides alignment of the received bit stream to 10b code-group boundaries

• 8b/10b Encoding and Decoding

2.BRC3

• Provides alignment of the received bit stream to 67b code-group boundaries

• 64B/67B Encoding and Decoding

Physical Protocol功能

该部分主要和底层的LVDS PHY 相连。

The Physical Layer protocol defines a full duplex LP-Serial and 8/16 bit LP-LVDS physical layer interface (link) between devices using unidirectional differential signals in each direction. It implements a protocol for link management and packet transport over a link.

Logical Protocol Layer逻辑层

基本属性

• Supports RIO Logical and Common Transport Layer functionality

• Supports both Input/Output Logical and Message Passing Logical protocols

• Supports up to 256 Bytes data payload

• Supports 64/128/256-bit internal data path

• Supports pipelined ULI

• Supports all transport sizes (DevID 8/DevID 16/DevID 32)

• Supports 34-bit and 50-bit (hardware configurable) addressing

• Supports hardware-configurable outstanding unacknowledged RIO transactions

• Supports all transaction flows and all priorities

• Supports encapsulation of RIO packet

基本功能:

The Logical Layer implements the logical and transport layer protocols. It controls the ordering of the received and transmitted packets and exchanges flow control information with the

Logical Layer of the device on the other side of the link.

1.Sends and receives packets between Physical Layer and ULI controller

2.Controls the ordering of the received and transmitted packets

3.Exchanges flow control information with the Logical Layer of the device on the other side of the link

RAB (RapidIO to AXI Bridge )介绍

其实RAB 这个部分GRIO部分容易明白,他的功能主要实现的是下面一些传输功能,特别时一些传输映射窗口的设置容易让人比较混乱。对应RAB 后续的文章描述会说明,主要会分为初始化、 PIO设置(APIO和RIO映射关系的设置),DMA操作、Message 生成和处理几个部分来说。

The AXI-RIO Bridge connects to RapidIO on one side and AMBA sub system on the other side. The following types of transfers are supported

1.AXI PIO (AXI Slave): Request is transferred from AXI to RapidIO. The bridge acts as AXI Write/Read Slave and RapidIO Initiator.

2.RIO PIO (AXI Master): Request is transferred from RapidIO to AXI. The bridge acts as RapidIO Target and AXI Write/Read Master. Additionally it handles optional Inbound and Outbound Messaging.

3.Write DMA (optional): Data is transferred from AXI to RapidIO. The bridge acts as AXI Read Master and RapidIO Write Initiator

4.Read DMA (optional): Data is transferred from RapidIO to AXI. The bridge acts as RapidIO Read Initiator and AXI Write Master.

5.Data Message (Optional): For Inbound Data messaging Bridge acts as RapidIO target and AXI Write Master. It also sends out responses towards RapidIO Fabric as RapidIO Initiator. For Outbound Data message it acts as AXI Read Master and RapidIO initiator.

6.Doorbell (Optional): For Inbound DB Bridge acts as RapidIO target and optionally either as AXI Write Master or APB CSR Slave or none (generates physical signal for Inbound DB). For Outbound Doorbell, it acts as APB CSR Slave and RapidIO initiator.

7.Data Stream (Optional): For Inbound Data Stream Bridge acts as RapidIO target and AXI Write Master. For Outbound Data Stream it acts as AXI Read Master and RapidIO initiator.In addition, RapidIO Configuration Space and device specific Control/Status/Debug register can be accessed by either RapidIO Host through RapidIO link, or AXI Master through AXI Write/Read

Slave Interface (or APB interface)

我使用IP 中的RIO 配置

对应初始化程序调用为rab_init函数对IP进行初始化,其中很重要的一部分就是对应RAPIDIO的地址映射关系。根据RAPIDIO的地址将传输数据传出或者写入内存空间,BAR 的配置和地址映射有一定关系。

PIO 空间是什么

PIO名词解释 :Programmable Input/Output

RIO名词解释: Rapid IO Interconnect

我使用的IPPIO分为AXI PIO 和 RIO PIO 模式。

1.AXI PIO (AXI Slave) 进行的是对外写操作,AXI Slave 能监听总线的状态,将对应映射地址写操作的内容通过RAPIDIO对外输出,或者是读操作发起对外RAPIDIO的读输出。

2.RIO PIO (AXI Master)外部RAPIDIO的对芯片的读写操作,如果是处理器地址将根据映射关系通过AXI的主对本芯片的内部空间进行读写操作。

大体上看AXI 和RIO 都是进行相关读写(细节有所不同后续有时间细化相关差异)

RAPIDIO 地址和AXI总线地址映射关系(AXI PIO Mode)

RAPIDIO 能够机进行AIX总线地址直接读写,RAPIDIO上发送的地址和访问AXI 总线地址间是有一定关系的,对应的关系设置如下图是通过寄存器设置。

AMBA域中的地址需要映射到RapidIO中对应的地址域,反之亦然,用于 PIO 和 DMA 操作。这是使用地址完成的由软件设置的映射表。例如,当 AXI 主设备发送读/写请求目标为RAB,AXI master指定的地址为AXI slave地址。这RAB 逻辑检查地址映射表,以确定 AXI 地址是否已被映射到 RapidIO 地址。如果已经映射了,那么对应的RapidIO地址就是计算并用于在 RapidIO 链路上生成读/写/维护事务。RAB 支持 34 位({xamsbs,地址})和 50 位寻址({xamsbs,扩展地址,地址})。默认情况下,所有传输都是 34 位寻址。一旦 PELLCCSR配置为选择 50 位地址,然后将使用 50 位寻址。数据包格式与不支持同时混合本地物理地址(34 位和 50 位)字段。注意:支持 50 位寻址是可选的,硬件可配置。

AXI PIO 中可以设置对应的区域的访问类型,比如NREAD NWRITE 或火灾SWRITE SREAD。

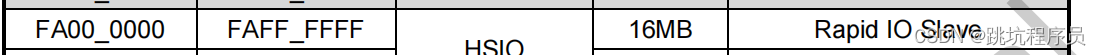

AXI PIO 地址对应的是Rapid IO Slave的空间地址。

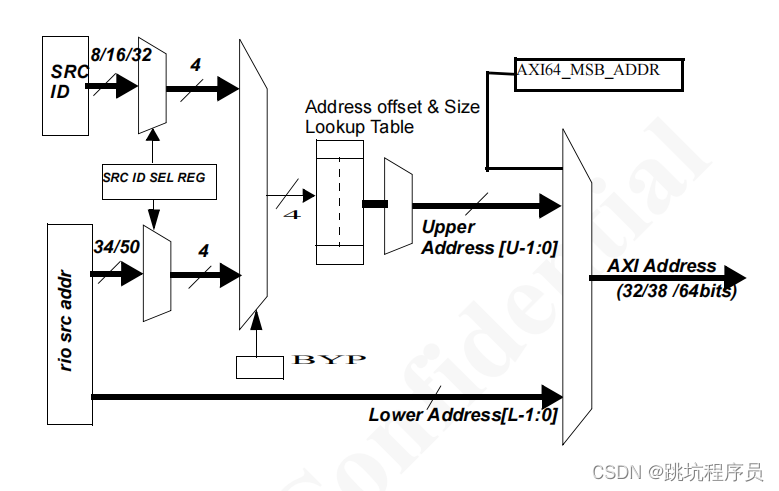

RAPIDIO地址对应AXI地址转换(RIO PIO Mode)

需要特殊注意的地方LCSBA1CSR 可能会影响到RIO PIO 的空间

Local Configuration Space Base Address (LCSBA0CSR,LCSBA1CSR),该部分将一段的RAPIDIO空间用于访问RAPIDIO本地寄存器。该空间可能和RPIO的空间重合,所以当出现部分RPIO 不能访问的时候需要注意是不是和这两个寄存器空间有冲突。

RPIO

相关的内容在“Address Mapping Scheme”章节。

我使用的芯片上对于从 RapidIO 域到 AMBA 域的事务,使用以下机制。

1.根据寄存器 RAB_AMAP_RPIO_BYPS 的设置,如果位 [0],则使能在 4 位从地址将用于选择地址偏移和大小查找寄存器。否则使用 RIO 数据包的传入源 ID 的 4 位。

2.当旁路使能打开时,34 位地址或 50 位地址中的哪 4 位将被用于从地址偏移和大小查找寄存器中进行选择的地址由 SRC_ID_SEL 寄存器的设置决定。

3.当旁通使能关闭时, 8/16/32 位的 Source ID 中的哪 4 位是应使用的传入数据包由“RIO-PIO 地址映射 LUT 索引”。

4.地址偏移量和大小查找表中的每个条目都有窗口大小和上地址偏移值。支持1M到2G的窗口大小。基于窗口大小字段在选定的表项中,高位地址偏移位的部分或全部位用于形成上 AXI 地址。来自 RIO 的低地址位作为 AXI 地址传递,基于窗口大小。

RAB 定义了 16 组寄存器来形成 AXI 地址偏移和大小表, 每个偏移量可以启用或禁用。

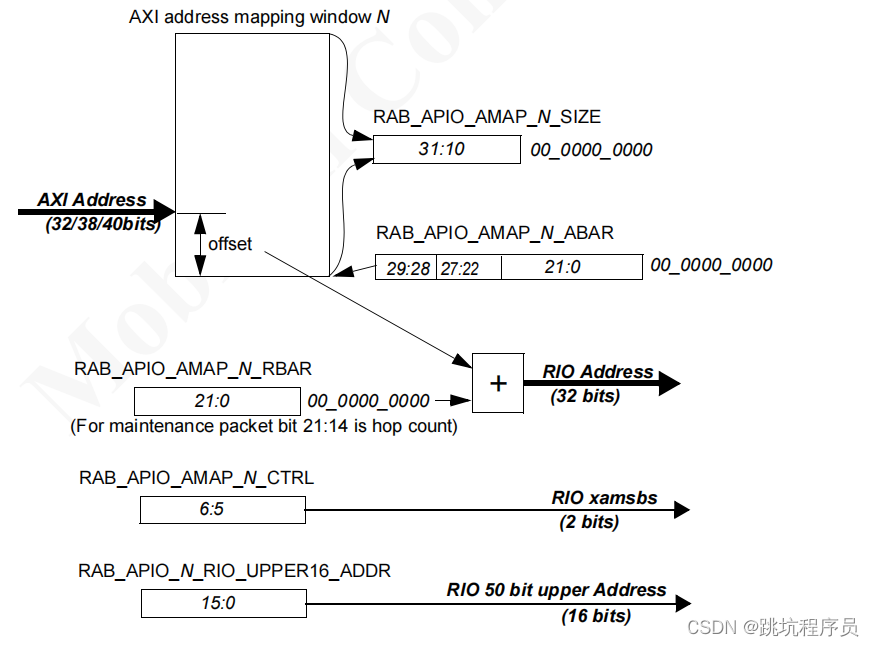

AXI 地址对应RAPIDIO地址转换(AXI PIO Mode)

提供了多个窗口用于将事务从 AXI 映射到 RapidIO。软件可以通过编程相应的窗口来配置每个窗口的大小和位置AMBA 地址映射寄存器组。当 AXI 总线上接收到读/写请求时,检查请求的地址以找出它是否位于 AMBA 中编程的窗口之一的基数和大小内地址映射寄存器。如果匹配,则计算相应的 RapidIO 地址根据的寄存器RAB_APIO_AMAP_N_RBAR 和读/写具有计算地址的交易在 RapidIO 链接上发送。对于维护读/写请求,将使用 RAB_APIO_AMAP_N_RBAR 的位 21:14用于传出请求数据包中的跳数字段。位 14:0 将用于计算config_offset 字段。一个映射窗口在 AMAB 和 RapidIO 地址空间中具有相同的大小,提供字节地址的一对一映射。窗口大小和起始地址边都在 1KB 边界对齐,或软件引用的页。

AMBA域中的地址需要映射到RapidIO中对应的地址域,反之亦然,用于 PIO 和 DMA 操作。 这是使用地址完成的由软件设置的映射表。 例如,当 AXI 主设备发送读/写请求目标为RAB,AXI master指定的地址为AXI slave地址。 这RAB 逻辑检查地址映射表,以确定 AXI 地址是否已被映射到 RapidIO 地址。 如果已经映射了,那么对应的RapidIO地址就是计算并用于在 RapidIO 链路上生成读/写/维护事务。RAB 支持 34 位({xamsbs,地址})和 50 位寻址({xamsbs,扩展地址,地址})。 默认情况下,所有传输都是 34 位寻址。 一旦 PELLCCSR配置为选择 50 位地址,然后将使用 50 位寻址。 数据包格式与不支持同时混合本地物理地址(34 位和 50 位)字段。

DMA可以不需要考虑APIO

DMA 的发送数据时,DMA本身有对应的相关RIO地址的配置。DMA发送时可以不配置APIO的窗口地址映射。

DMA读取时不需要考虑本芯片的RPIO

DMA进行读取的时候,当对端返回DMA读数据写入内存时。经过测试respons带数据返回的内容不受RPIO的接收窗口的限制。

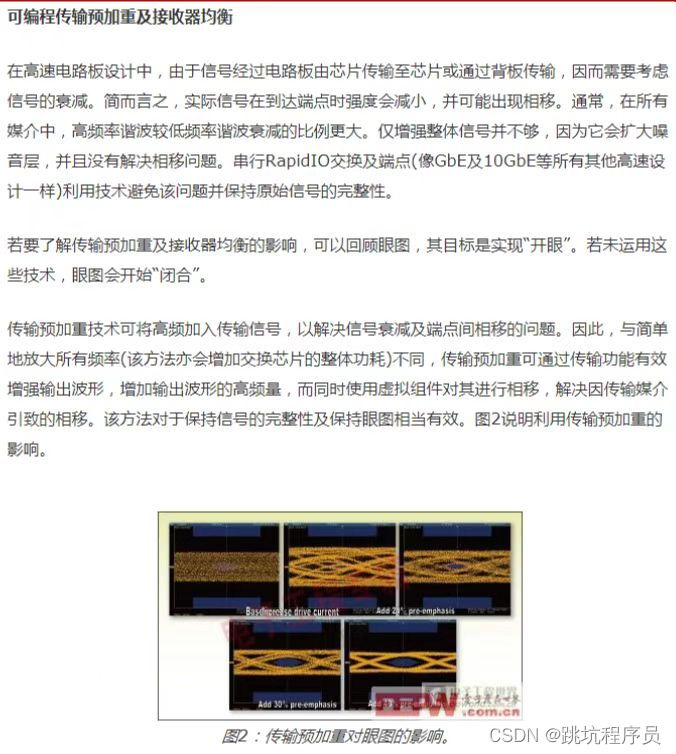

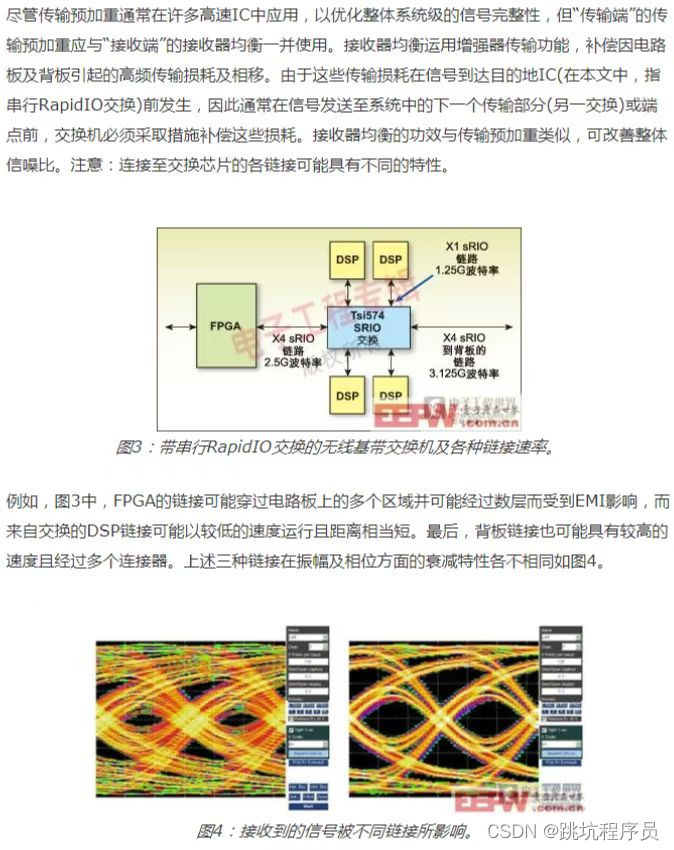

信号预加重

2995

2995

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?